- 热点文章

-

- 09-14关于高等职业院校弱电专业教改的探索

- 11-28东芝将在2009年CES带来新水平的前沿技术

- 11-28互联网:世界的镜子

- 11-28中美文化论坛研讨数字技术保护文化

- 11-28浅析“三鹿集团奶粉事件”危机根源

- 11-28新媒体的发展及其教育创新应用研究

- 11-28楼宇信息系统的现状与应用以及发展趋势

- 11-28中国2009世界邮展60城市巡邮漯河站启动

- 11-28打造焕发生命活力的教育时空

- 11-28观察中国管理教育30年

- 11-28驾驭论:科学发展的新智囊

- 11-28软着陆将解读中国管理国际化新走势

- 11-28创建中国水电国际化强势品牌

- 11-28管理科学进入新观察时代

- 11-28全球化传播语境下的家国建构

- 11-28网络民主对公民社会建设的影响研究

- 11-28奥运后中国酒店业的发展分析

- 11-28国家创新系统下的大学科研管理研究

- 11-28高校数字图书馆建设及服务模式探讨

- 11-28非均衡理论及我国房地产市场供求

- 11-28绿色、安全和通讯是汽车电子的未来

- 11-28敦煌莫高窟将为游客建"数字洞窟"

- 11-28思科新软件平台帮媒体公司建社交网络

- 11-28苹果乔布斯:用13年给IT业洗一次脑

- 11-28海外传真:2008年数字印刷市场回顾

- 11-28东芝将在2009年CES带来新水平的前沿技术

- 11-28互联网:世界的镜子

- 11-28中美文化论坛研讨数字技术保护文化

- 11-28故宫国图面临“数字化”难题 缺乏专门人才

基于 FPGA 的大容量瞬态信号存储测试系统 *

2024-05-06 10:43:00 来源:优秀文章

摘 要 :针对触发式瞬态信号存储测试系统的不足,基于 FPGA 设计了连续采集模式的大容量瞬态信号存储测试系统,由 FPGA 控制高速 AD 转换芯片对 12 路冲击加速度信号进行连续同步采集,最高采样频率为 100kHz,并实时将采集到的数据连续存储到大容量 FLASH ;系统内部集成网络接口芯片,上位机可以通过 RJ45 接口快速读取测试系统中存储的数据 ;测试系统在水平碰撞试验中进行了应用,通过试验验证了系统的有效性。

关键词 :FPGA ;存储测试 ;NAND FLASH

中图分类号 :TM930.2 文献标识码 :B 文章编号 :1671-2064(2023)10-0043-03

0引言

存储测试系统是一种用于检测、记录目标对象在运行或爆轰过程中各项性能参数的设备。在数据采集结束后,可以通过数据回读得到试验数据,进行离线数据分析研究。瞬态冲击信号的有效持续时间约在 10ms 以内,频响可达 20kHz,针对这种信号的测试,通常要求数据采集系统的采样频率达到 100kHz,为了节省存储空间,大多采用负延时触发的方式存储有效数据 [1-6],当检测到冲击信号超过预设值的触发阈值时才开始存储采集到的数据,这种存储方法所需的存储容量小,但抗干扰能力差,触发阈值设置不合理时容易误触发,导致不能获取有效试验数据。

对此,本文提出一种基于 FPGA 连续采集模式的大容量瞬态信号存储测试系统,采用 16GB 大容量 NAND FLASH 作为存储介质,系统上电后,由 FPGA 控制 12 路高速 A/D 芯片进行高速同步采集,并连续将采集到的数据存储到 NAND FLASH,存储时间可以覆盖整个试验过程,通过这种测试法可以有效避免触发阈值设置不合理带来不能获取有效数据的风险。由于系统采样频率高,且存储了整个试验过程的数据,存储的数据量较大,为了缩短数据回读时间,本文采用数据传输速度较快的网口接口芯片将NAND FLASH 中的数据回读到上位机,经试验验证,本文设计的存储测试系统可以有效获取瞬态冲击数据。

1系统架构及其工作原理

测试系统架构如图 1 所示,加速度计的信号经信号调理电路调理后进入 A/D 芯片,FPGA 控制 A/D 芯片对12 路冲击加速度信号进行同步采集,并将采集到的数据实时写入 NAND FLASH 大容量存储器。试验完成后,上位机通过 W5300 网络接口芯片控制 FPGA 读取 NAND FLASH 中存储的试验数据。

图1 测试系统架构图

2硬件与软件设计

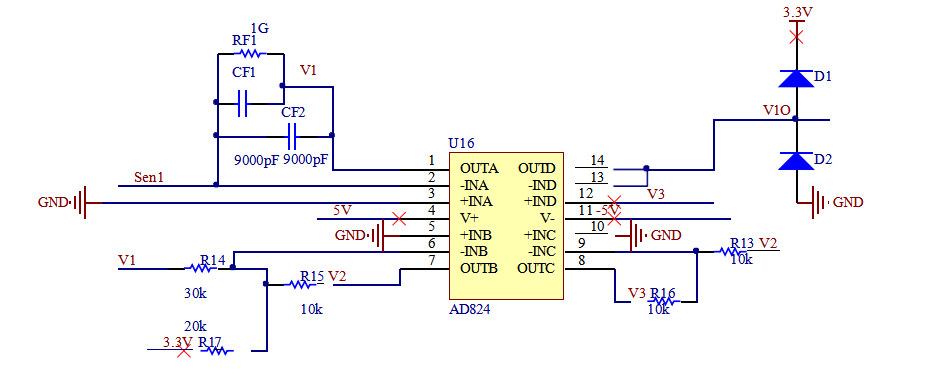

2.1信号调理电路设计

针对冲击加速度信号,一般采用压电型加速度计进行测量,采用 AD824 运算放大器设计了加速度计信号调理电路(如图 2 所示),其主要功能是将压电型加速度计输出的电荷信号转换为模拟电压信号。由于所选 AD 只能采集直流信号,因此,将调理后输出的模拟信号进行了电压抬升,抬升后的模拟信号的幅值为 0V ~ 3.3V。

图2 信号调理电路原理图

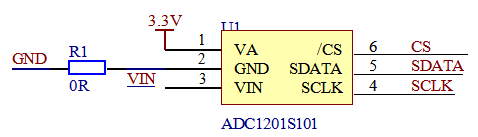

2.2A/D 芯片硬件接口设计

冲击信号持续时间短、频率高,其有效持续时间通常在 10ms 以内,频响范围为 0kHz ~ 10kHz,对此,测试系统的采样频率设计为 100kHz,采用 12 位串行 A/D 芯片 ADC121S101 数据采集执行器件,该芯片最高采用频率可达 1Msps,满足系统需求,A/D 芯片硬件接口电路如图 3 所示。

图3 A/D芯片硬件接口电路

芯片片选引脚(CS)、数据引脚(SDATA)和时钟引脚(SCLK)直接与 FPGA 连接,VIN 为模拟信号输入引脚,芯片 GND 通过 0Ω 磁珠连接到信号地,0Ω 磁珠主要用于消除高频干扰。

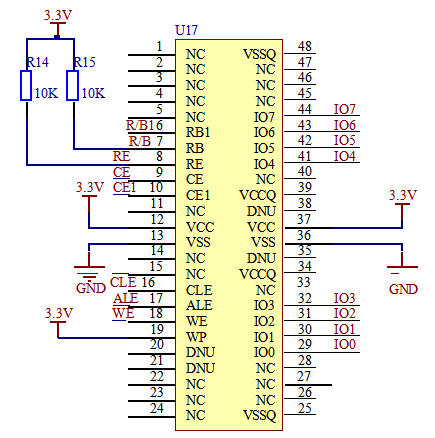

2.3NAND FALSH 存储器硬件接口设计

存储测试系统以 100kHz 的采样频率对 12 路冲击加速度信号进行同步连续采集,并实时存储采集到的数据,考虑到数据量较大,选用美星公司的 MT29F128G08 存储芯片对数据进行实时存储,该芯片的存储容量为 16GB,可以连续存储 2h 的数据,充分覆盖试验时间,确保试验有效数据完全存储,存储器硬件接口电路如图 4 所示。

图4 存储器硬件接口电路

MT29F128G08内部由两组存储模块组成,每组存储模块的容量为 8GB,两组存储模块共用命令寄存器使能引脚(CLE)、地址寄存器使能引脚(ALE)、写使能引脚(WE)、读使能引脚(RE) 和 8 位复用 I/O口,片选引脚(CE)和工作状态引脚(R/B)分别单独引出,工作状态引脚通过10K电阻上拉后与 FPGA 连接,其余引脚直接连接到 FPGA。

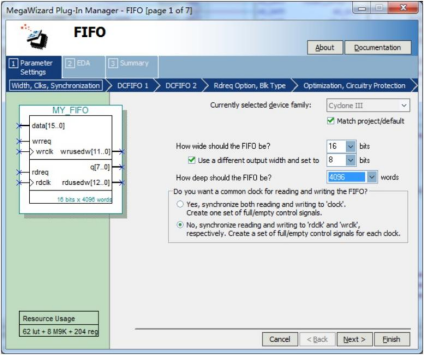

2.4 FIFO 接口设计

NANDFLASH 采用页编程机制,页编程时间约1ms,在页编程时间内采集到的数据只能暂存到FIFO中,待页编程完之后再写入 NANDFLASH,为了节约硬件开销,利用 FPGA内部集成的参数设置模块库(LPM),建立异步 FIFO,FIFO 容量为 4KB,如图 5所示。

图5 用LPM生成FIFO示意图

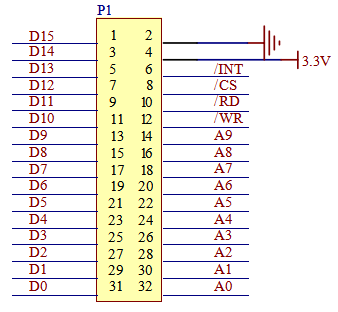

2.5 网络接口芯片硬件电路设计

存储测试系统采用 HS-Nm5300A以太网传输模块实现上下位机的网络通信,该模块基于以太网传输芯片设计,W5300内部集成 10/100M以太网控制器,MAC 和 TCP/IP 协议栈,可以简单快捷地实现网络连接与传输,且自带RJ45 接口,可直接连接网线,最高传输速率可达 80Mbps,HS-Nm5300A以太网传输模与 FPGA 接口电路如图 6 所示。

图6 HS-Nm5300A以太网传输模接口电路

W5300 芯片的引脚通过模块上的双排插针引出,可直接与 FPGA 引脚连接,其中RST 为复位引脚,FPGA 将RST 拉低 2ms即可对 W5300 进行复位 ;D0 ~ D15 为16位数据工作总线,A0 ~ A9 为 10 位地址总线,通过写相应寄存器的值,系统将 W5300 配置为 UDP 传输模式。

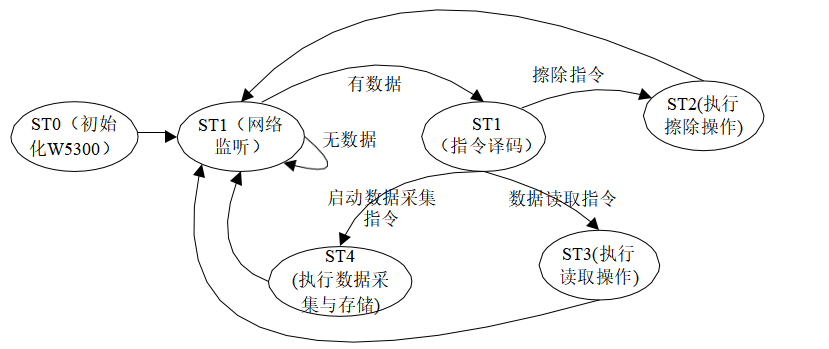

2.6 FPGA 状态机设计

测试系统包含 :初始化 W5300、网络端口监听、数据采集与存储、上传测试数据、擦除存储器数据 5 个状态,初始化 W5300 操作主要是对 W5300 寄存进行相应配置,初始化完成后开始监听网络中是否有上位机下发的指令,若收到上位机指令,则根据指令执行相应操作,执行完后返回网络端口监听状态,否则继续监听,状态机流程图如图 7 所示。已经有相关研究[7-8] 介绍 W5300 初始化和 NAND FLASH 存储器具体方法,本文不再论述。

图7 状态机流程图

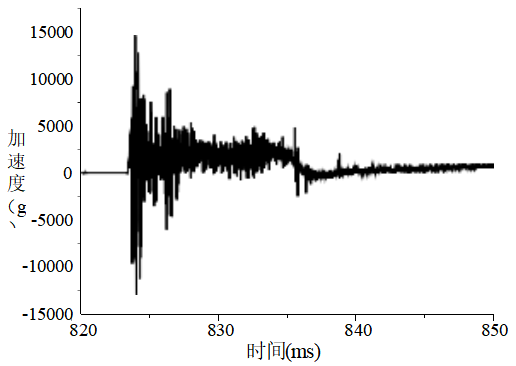

3 试验应用

系统在水平试验中进行了应用,对碰撞产生的冲击加速度信号进行测试,测试结果如图8 所示。从图8 可以看出,本文设计的存储测试系统可以有效冲击信号。

图8 冲击信号测试结果

4结论

针对触发式存储测试系统的不足,本文提出一种基于FPGA的瞬态信号大容量存储测试系统,采用16GB 大容量 NANDFLASH 作为存储介质,可以将整个试验过程的数据进行存储,通过这种存储方法可以有效避免触发阈值设置不合理带来不能获取有效数据的风险。由于系统存储了大量的无效数据,为了提高数据回读效率,采用了数据传输速度较快的网口接口芯片将 NANDFLASH中的数据回读到上位机。经试验验证,本文设计的存储测试系统可以有效获取瞬态冲击数据。

参考文献

[1]郭建,王文廉,张志杰.四通道高速同步采集多次触发存储测试系统[J].核电子学与探测技术,2010, 30,(6):782-786.

[2]刘泽鹏,苏新彦,王小亮,等.一种通用高精度存储式冲击波测试系统设计[J].单片机与嵌入式系统应用,2021,(1):54-56.

[3]牛明杰,孔德仁.侵彻弹弹体应变存储测试系统设计[J].电子测量技术,2019,42(6):42-47.

[4]魏明生,刘莹,警斌,等.基于CPLD高速信号存储测试系统的设计[J].微计算机信息,2008,24(10):189-193.

[5]周继昆,张荣,李思忠.基于CPLD的多路瞬态冲击信号存储测试系统设计[J].计算机测量与控制,2016,24(7):21-23.

[6]李詧森,王代华,于建军,等.多通道存储式坑道冲击波测试系统设计[J].计算机测量与控制,2021,29(3):114-118.

[7]王雨婷,薛志超,文丰.基于W5300的以太网高速数据传输系统 设计[J].电子设计工程,2021,29(6):49-52.

[8]唐超.基于FPGA的NanFlash存储模块设计[J].科学技术创新,2021,(13):83-85.

Design of the Flash Storage Impulse Signal Measurement System Base on FPGA

ZHOU Jikun,ZHANG Rong,LI Chong,HUANG Haiying,WANG Junping

(Institute of Systems Engineering, China Academy of Engineering Physics, Mianyang Sichuan 621999)

Abstract:In view of the shortage of the trigger mode impulse signal measurement system, a continuous acquisition mode flash storage impulse signal measurement system is designed based on FPGA. The FPGA controls the 12 channel high-speed AD chip to collect shock signal continuously, and the maximum sampling frequency can reach to 100kHz. The collected data are stored in NAND FLASH in real time continuously. The upper computer can quickly read the data stored in the NAND FLASH through RJ45 port with a network interface chip embed in measurement system. The measurement system is applied in the horizontal collision test, and the effectiveness of the system is verified.

Key words:FPGA;storage measurement;NAND FLASH